ACTF 2025 WriteUp-ezFPGA

推荐阅读Nepnep战队wp

1.获取加密逻辑

加密逻辑在ezFPGA\src\encryptor.sv文件中,可以将其转为C代码以便于阅读(ai大法)

1 |

|

总结为:

- 初始化

aa数组: 使用输入的FLAG参数填充aa数组的前l个元素,其余用 0 填充 - 线性变换 1 (

aa到ac): 使用系数ab进行滑动窗口计算 - 线性变换 2 (

ac到ae): 使用系数ad进行更复杂的基于块的变换 - 类 RC4 :

- KSA 使用密钥

db = "eclipsky"打乱数组ba - 伪随机生成一个密钥流

k - 混合为

密文[i] = 密钥流[i] + ae[i]

- KSA 使用密钥

2.获取密文

密文也就是af

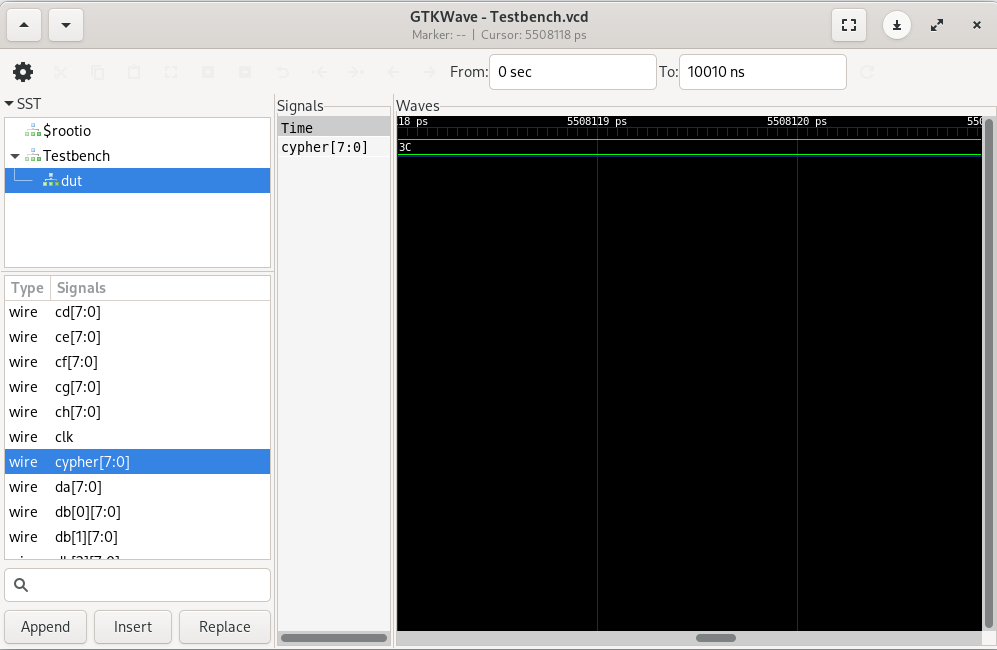

可以在Linux中用make wave等命令打开GTKWave,查看cypher信号的值,但是只能一个个显示,非常不方便

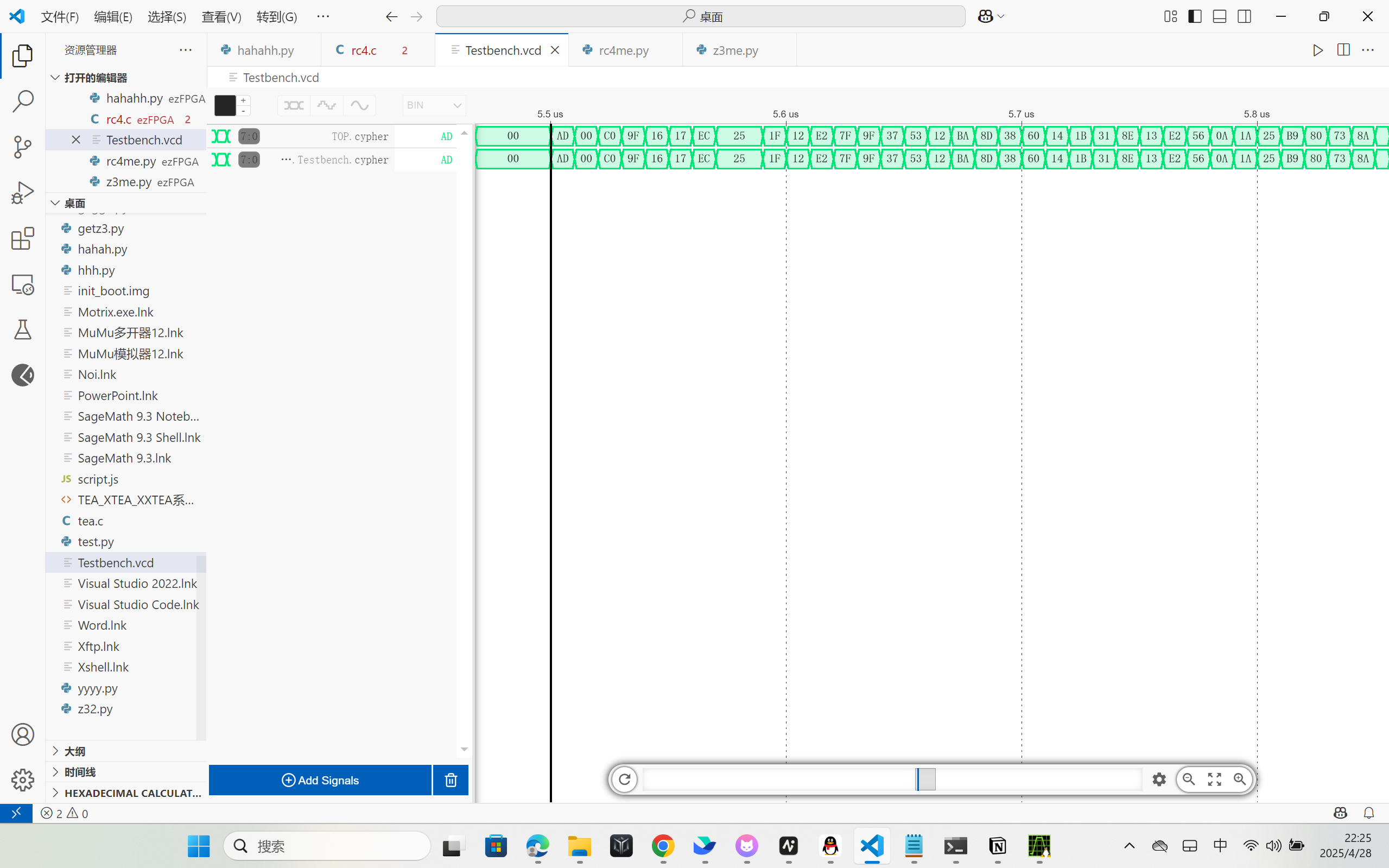

这里推荐在VScode中安装插件WaveTrace,将.vcd文件拖入其中即可查看

得到密文:

1 | ad 00 c0 9f 16 17 ec 25 25 1f 12 e2 7f 9f 37 53 |

(”25“占了两格长度,所以为两个数据)

3.求解RC4

1 |

|

1 | Recovered ae: |

4.求解flag

剩余部分我们可以使用z3约束求解,在这里可能会遇到一个问题,就是python默认是32位加法,而 Verilog 是 8位加法(自动取模256),所以记得每一步都强制 & 0xFF

1 | from z3 import * |

1 | Recovered FLAG: ACTF{RC4_4nd_FPGA_w4lk_1nt0_4_b4r} |

总结

这道题我本来的方向是偏了,转去研究FPGA的硬件知识了,后来也是在提取密文的部分因为工具(vsc插件)的问题导致了进度缓慢,总之一道题让我学到了很多

- 标题: ACTF 2025 WriteUp-ezFPGA

- 作者: mmj

- 创建于 : 2025-05-09 23:26:21

- 更新于 : 2025-05-11 23:36:36

- 链接: https://samzhaohx.github.io/2025/05/09/ACTF 2025 WriteUp-ezFPGA/

- 版权声明: 本文章采用 CC BY-NC-SA 4.0 进行许可。

评论